AI芯片体系架构和软件专题报告会

报告介绍

本次有关AI芯片体系结架构和软件的专题报告由北京大学梁云老师主持,参会分享的嘉宾来自清华大学、北京大学、南加州大学和中科院的计算所、信工所。

主要内容

AI算法涉及三个要素,分别是算法、算力和数据。该次报告会住哟啊关注算力部分。

本次会议主要内容是AI算法在芯片中执行涉及到的架构设计,计算加速,内存访问等。该方面的研究既需要懂上层应用算法,还要懂底层的体系架构,分享的内容较为干货,相关的研究成果发表在该各大顶会上,并且研究中的很多成果进行了开源。本次报告会的受众对象不仅可以让上层应用人员优化算法在底层的执行情况,而且让底层硬件设计人员受益,激发设计思路。

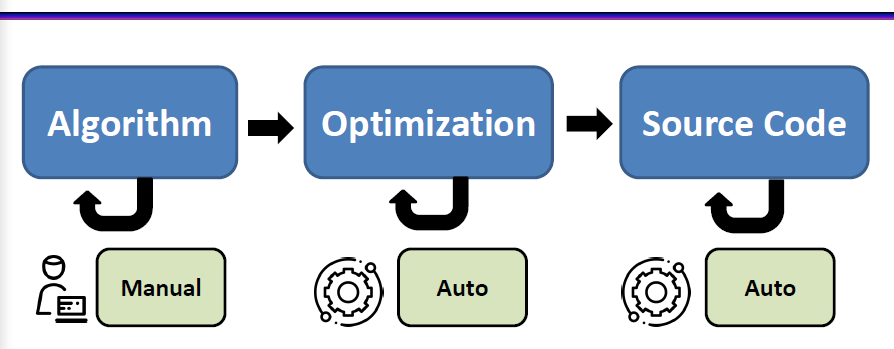

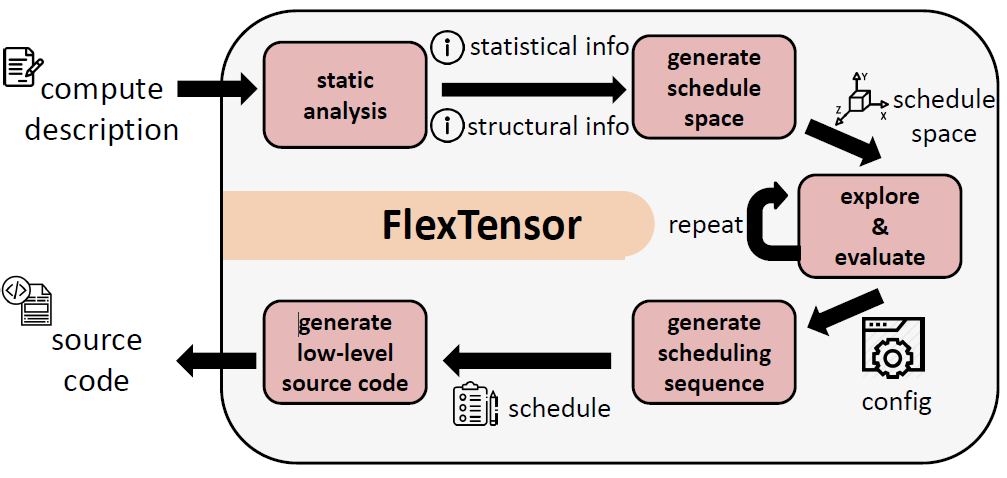

1. FlexTensor——北大梁云老师

AI中绝大部分算法都需要进行张量计算,也就是多维度的数组运算,如GEMM,Conv2d等等。目前很多提出来的算法框架,如AlexNet、GoogleNet,都以来张量计算。但是,这些张量计算底层运行的处理器多种多样,有Intel的,Invdia和Xlinx等。为此,这些异构系统开发了很多可用调用的Library,但这些工作开销时间打,并且需要很多的人力,无法跟上应用的需要。为此,本文设计了FlexTensor,一个调度框架,用于代码生产,可以自动优化,并且性能高,可移植。

其框架如上,工作流程如下图:

详细的内容可参考附件。

2. Interstellar——清华高铭宇老师

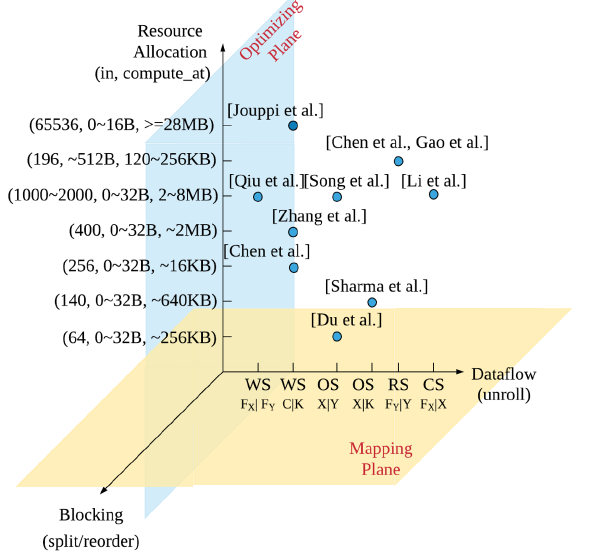

本文主要使用Halide的调度语言分析DNN加速器。

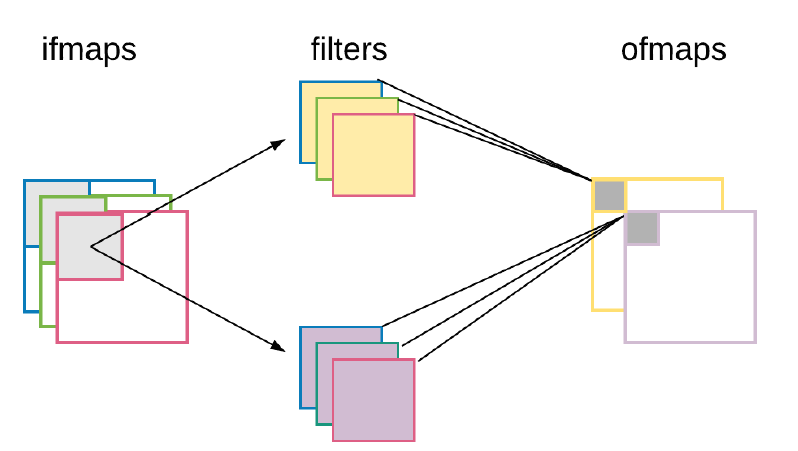

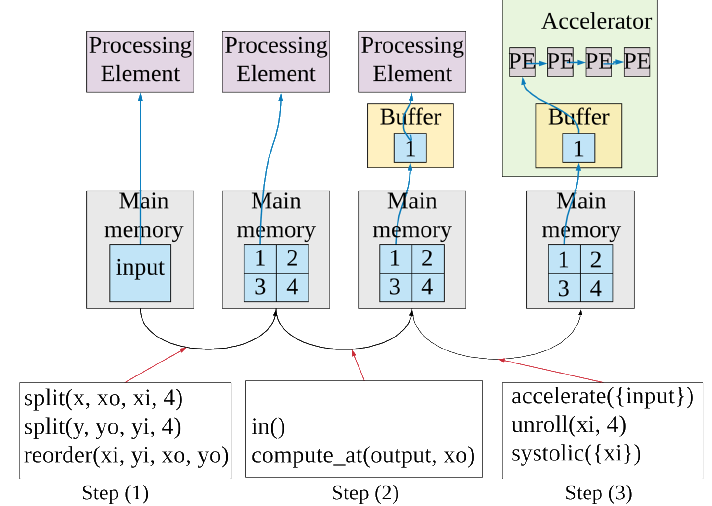

首先分析DNN计算的流程,分为三步:输入映射,过滤,输出映射。

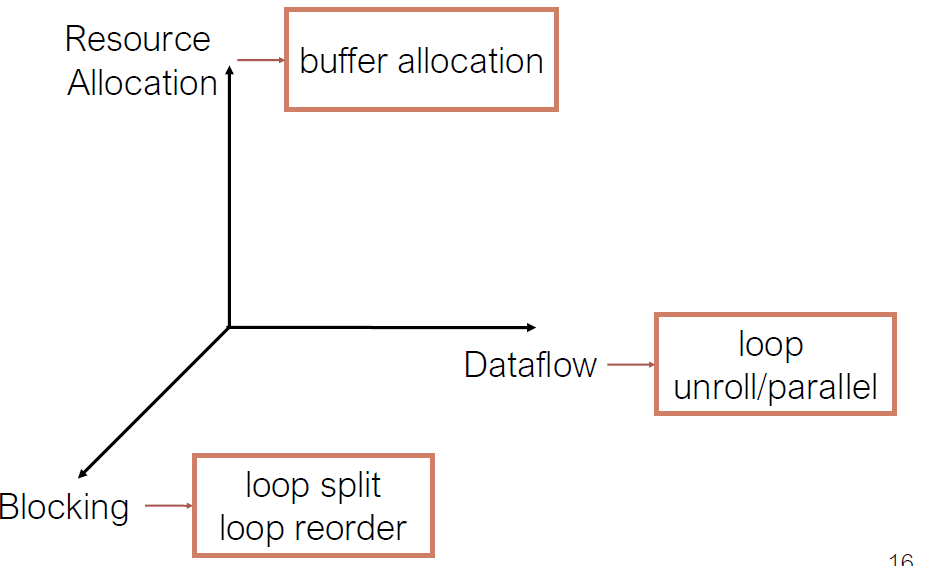

上述每个步骤中可以使用batch计算,对此可以使用三个维度表示

是红Haliide调度原语,其 在微处理器上调度数据流为:

得出结论:所有的加速器都可以归为Halide调度。

为此本文提出了Interstellar,,分许DNN加速器,详细的内容可以参考附件。

3. Praguue——南加州骆沁毅博士

本文提出了一个高性能的异构感知的异步去中心化的训练器

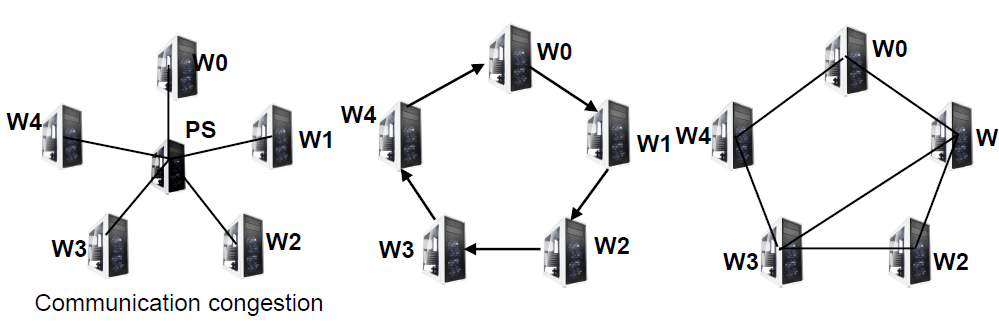

机器学习中大都采用分布式的训练,Workers需要处理不同的数据并进行同步,主要有三种方式:中心式,流水线式,非中心化的。

但是上述分布训练的架构存在worker工作慢,通信量大等其他问题。

对此,基于对worker分析,有可能同额外一个worker执行reduce操作;结合最近提出的算法:AD-PSGD,本文提出了Prague。详细内容参考附件。

4. 卷积加速器中的通信下届——计算所陈晓明老师

卷积神经网络使用较为频繁,如Alexnet,GoogleNet....,主要用于图像分类,目标识别,NLP等。

由于计算量的庞大,市场上出现了很多CNNs加速器,如使用cuDNN的GPU,FPGA专用加速硬件等。通过分析,CNN加速其的主要限制式内存瓶颈,内存访问消耗了大量的功率。

分析其中的矩阵乘法,优化后可以减少需要的内存容量,通过一系列计算得到通信下界。详细内容可以查看附件。

5. DNNGuard——信工所侯锐老师

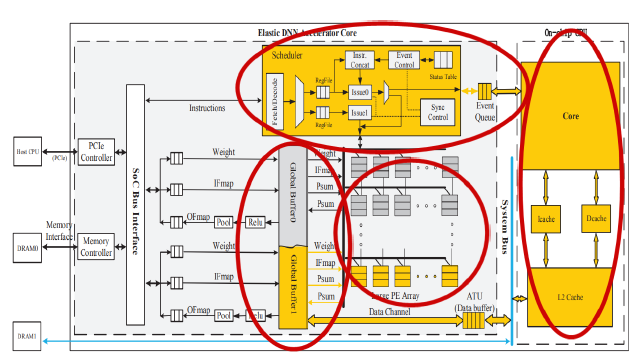

DNNGuard是一个用于DNN加速器抵抗对抗攻击的弹性架构。

现有的DNN加速器,对于对抗攻击防御,组要部署在GU,存在开销大,效率低,安全性不足的问题。

为此,需要设计一个新的DNN加速器,同时执行目标网络和检测机制。对此,本文提出了DNNGUard,该架构主要包含三特性:

(1)紧耦合的异构架构。

(2)任务级的通信和共享

(3)任务级的 同步和调度

同步和调度

详细设计可以查阅附件。